マーケットトレンド の ファンアウトパッケージング 産業

大きなシェアを占める高密度ファンアウト

- ミッドレンジからハイエンドのアプリケーションをターゲットとする高密度ファンアウトは、1mm2あたり6~12I/Oで、ライン/スペースは15/15μm~5/5μmである。高密度ファンアウトパッケージングは、携帯電話パッケージングのフォームファクターと性能要件に対応するために普及しました。この技術の主な構成要素は、再配分層(RDL)メタルとメガピラーめっきです。

- TSMC の InFO 技術は、高密度ファンアウトの最も顕著な例の 1 つです。この技術は、アプリケーション・プロセッサ(AP)など、よりピン数の多いアプリケーションを対象としている。同社はFO-WLP分野をinFO-Antenna-in-Package (AiP)やinFO-on-Substrateなどの技術に拡大する計画である。これらのパッケージは自動車、サーバー、スマートフォンに使用される。アップルはこの新技術をいち早く採用した企業のひとつで、2016年後半に発表されたiPhone 7のA10アプリケーション・プロセッサーに採用された。

- このような利点から、2021年12月、クアルコムとメディアテックの両社は、iPhoneチップのパッケージにTSMCのInFO_PoP技術を利用するアップルの足跡をたどり、自社のフラッグシップ・スマートフォン・アプリケーション・プロセッサの製造にファンアウトPoPを採用することを検討した。

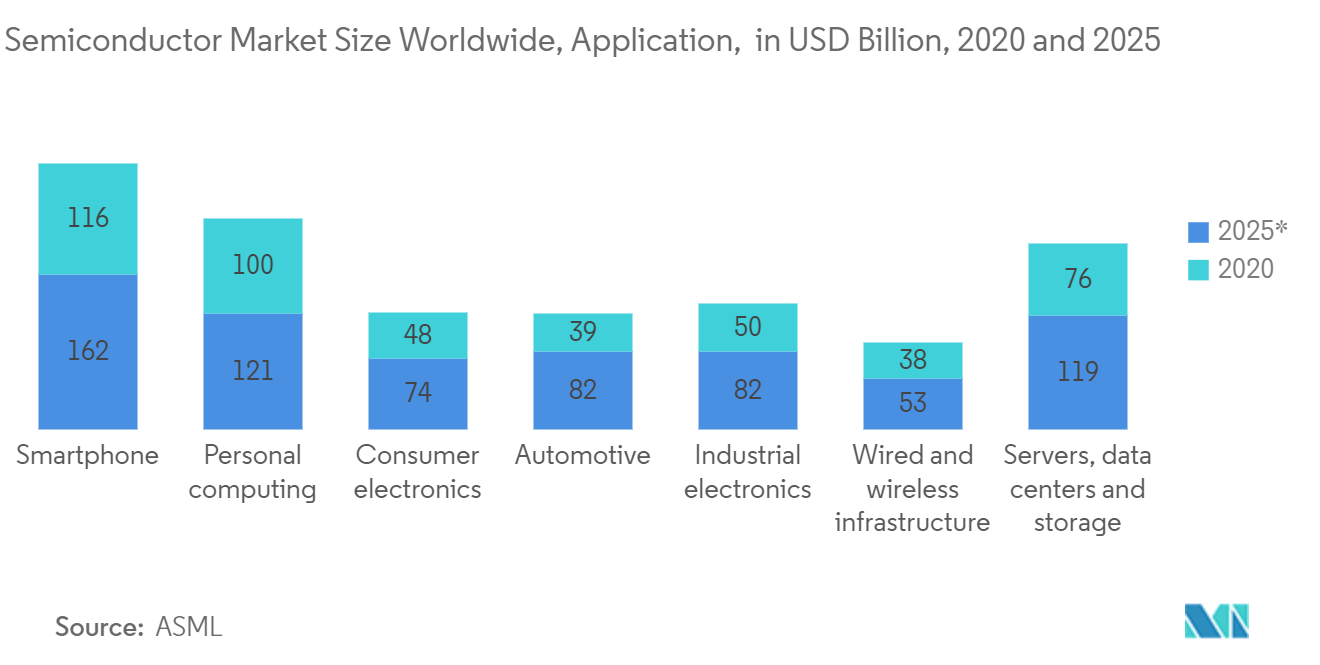

- さらに、半導体市場の成長と高密度ファンアウト・パッケージング・ソリューションの開発が、予測期間中の市場成長を促進すると予想される。例えば、2021年7月、世界有数の複合回路メーカーおよび技術ソリューションプロバイダーであるChangdian Technologyは、XDFOIチップ用の超高密度ファンアウトパッケージングオプションの全ラインの正式導入を明らかにした。

- 高密度ファンアウト・ウェハーレベル・パッケージング(FOWLP)の製造方法においても進歩が見られます。信頼性、エネルギー効率、デバイス速度、多機能集積を向上させながら、チップサイズ/高さを縮小し、製造コストを削減するソリューションが開発されている。例えば、SPTSテクノロジーズは、高密度ファンアウト・ウェーハレベル・パッケージングなどの高度なパッケージング・スキーム向けに、複数のプラズマエッチングおよび成膜プロセス技術を大手半導体パッケージング企業に提供している。

- さらに、高密度ファンアウト(HDFO)パッケージは、トール銅(Cu)ピラーやスルーパッケージビア(TPV)などのスルーモールド相互接続や高度なフリップチップパッケージング技術を使って3D構造を作成する能力と相まって、ウェーハレベルプロセッシングの製造能力によって、これらの小型化ニーズに対応することができます。

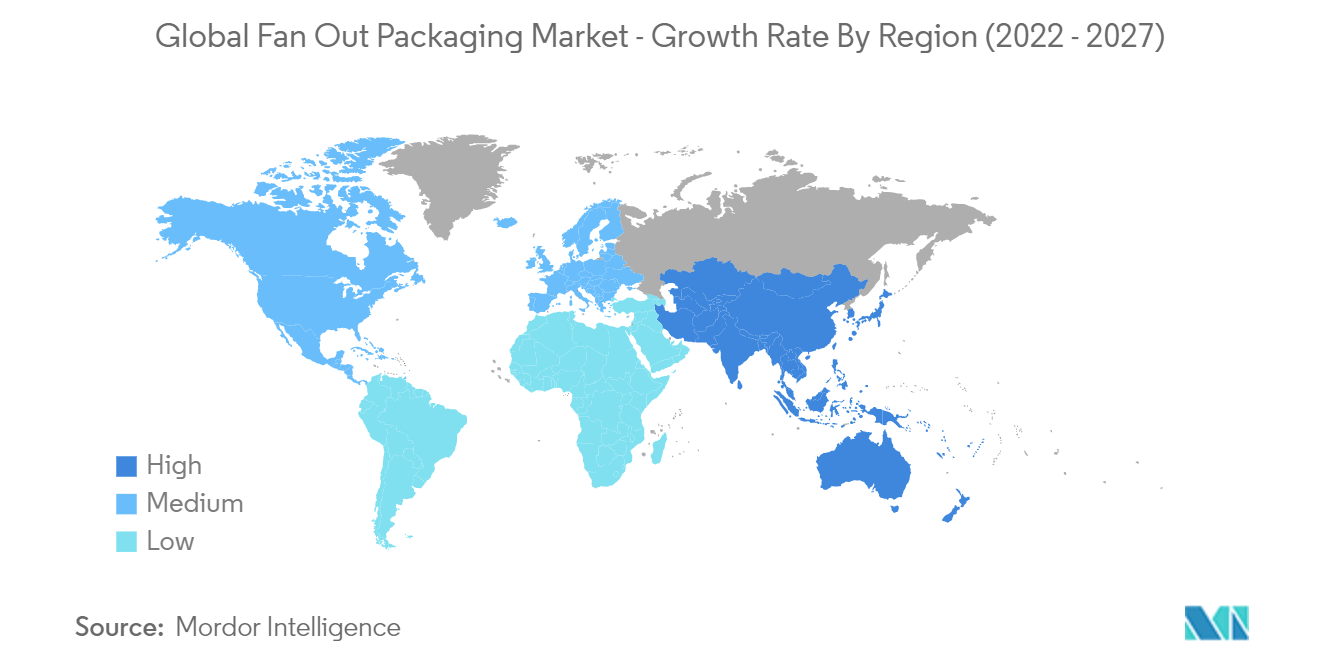

台湾が市場で大きなシェアを占める

- 台湾には主要な半導体製造企業があり、特にPLPのような先進的な半導体パッケージの需要に拍車をかけている。政府系シンクタンクの科学技術国際戦略センターによると、台湾の生産高は2021年に25.9%増の1470億米ドルに成長すると見込まれている。

- 半導体産業協会(SIA)によると、アジア太平洋地域は世界の半導体売上高の50%以上を生み出しており、このことは台湾のベンダーに、半導体アプリケーションの増加にFOWLPを供給する機会を提供している。

- 台湾の大半の企業はファンアウトパッケージの生産能力を拡大しており、これは輸出を増加させ、地元市場の発展に貢献すると期待されている。例えば、最近ファウンドリー産業への復帰を発表したインテルは、同時にニューメキシコ州に35億米ドルを投資し、2022年後半に操業を開始する半導体パッケージ工場を建設する予定である。

- さらに、2021年6月、純粋半導体後工程(OAST)のASEは、半導体の需給不足に対応するため、高度なパッケージング設備への投資を開始した。ハンミセミコンダクタからWLP、PLPプロセス用の半導体製造装置を大量に購入し、拡大を加速している。

- また、第5世代(5G)無線通信や高性能コンピューティングの市場拡大により、メーカー各社は新たな技術開発に取り組んでいる。例えば、TSMCは高密度ファンアウト分野の唯一のリーダーとして、FO-WLP分野をinFO-Antenna-in-Package (AiP)やinFO-on-Substrate (oS)のような技術に拡大することを計画している。