Markt-Trends von Fan-Out-Verpackung Industrie

High-Density-Fan-Out, um einen signifikanten Anteil zu halten

- Der High-Density-Fanout ist für Anwendungen im mittleren bis oberen Preissegment gedacht und hat zwischen 6 und 12 I/Os pro mm2 und zwischen 15/15 μm und 5/5 μm Leitung/Abstand. Fan-Out-Verpackungen mit hoher Dichte erfreuen sich immer größerer Beliebtheit, da sie den Formfaktor- und Leistungsanforderungen für Mobiltelefonverpackungen gerecht werden. Zu den wichtigsten Bausteinen dieser Technologie gehören Redistribution Layer (RDL)-Metall und Mega-Pillar-Plating.

- Die InFO-Technologie von TSMC ist eines der bemerkenswertesten Beispiele für Fan-Out mit hoher Dichte. Diese Technologie zielt auf Anwendungen mit höherer Pinzahl ab, beispielsweise auf Anwendungsprozessoren (AP). Das Unternehmen plant, sein FO-WLP-Segment auf Technologien wie inFO-Antenna-in-Package (AiP) und inFO-on-Substrate auszudehnen. Diese Pakete werden in Autos, Servern und Smartphones verwendet. Apple gehörte zu den ersten Anwendern dieser neuen Technologie und nutzte sie im A10-Anwendungsprozessor des Ende 2016 eingeführten iPhone 7.

- Aufgrund dieser Vorteile erwogen Qualcomm und MediaTek im Dezember 2021 die Einführung von Fan-out-PoP bei der Produktion ihrer Flaggschiff-Smartphone-Anwendungsprozessoren und traten damit in die Fußstapfen von Apple, das die InFO_PoP-Technologie von TSMC zur Verpackung seiner iPhone-Chips nutzte.

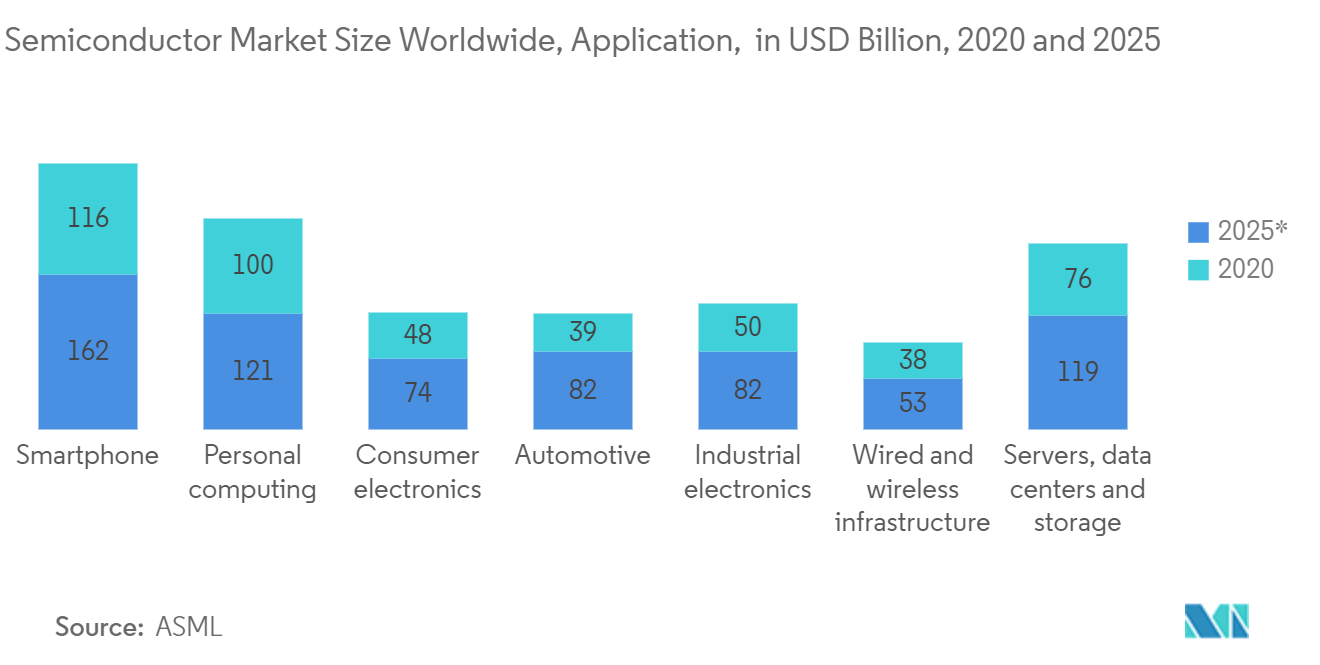

- Darüber hinaus wird erwartet, dass das Wachstum des Halbleitermarktes zusammen mit der Entwicklung hochdichter Fan-Out-Verpackungslösungen das Marktwachstum im Prognosezeitraum ankurbeln wird. Beispielsweise gab Changdian Technology, der weltweit führende Hersteller von kombinierten Schaltkreisen und Technologielösungsanbieter, im Juli 2021 die offizielle Einführung der gesamten Reihe von Fan-out-Gehäuseoptionen mit sehr hoher Dichte für XDFOI-Chips bekannt, die eine kostengünstige Bereitstellung ermöglichen sollen. effektive, hochdichte Konnektivitäts-, Hochintegrations- und Hochzuverlässigkeitslösungen für die heterogene Chip-Integration.

- Auch bei der Herstellungsmethode für High-Density Fan-Out Wafer Level Packaging (FOWLP) wurden Fortschritte erzielt. Es werden Lösungen entwickelt, um die Chipgröße/-höhe zu reduzieren und die Produktionskosten zu senken und gleichzeitig die Zuverlässigkeit, Energieeffizienz, Gerätegeschwindigkeit und Multifunktionsintegration zu verbessern. Beispielsweise bietet SPTS Technologies führenden Halbleiterverpackungsunternehmen mehrere Plasmaätz- und Abscheidungsprozesstechnologien für fortschrittliche Verpackungsschemata wie das hochdichte Fan-out-Wafer-Level-Packaging an.

- Darüber hinaus können High-Density-Fan-out-Pakete (HDFO) diesen Anforderungen der Miniaturisierung gerecht werden, indem sie über Fertigungsmöglichkeiten für die Wafer-Level-Verarbeitung verfügen und gleichzeitig 3D-Strukturen mithilfe von Durchformungsverbindungen wie hohen Kupfersäulen (Cu) und Durchgangsgehäusen erzeugen können Vias (TPVs) und fortschrittliche Flip-Chip-Gehäusetechnologien.

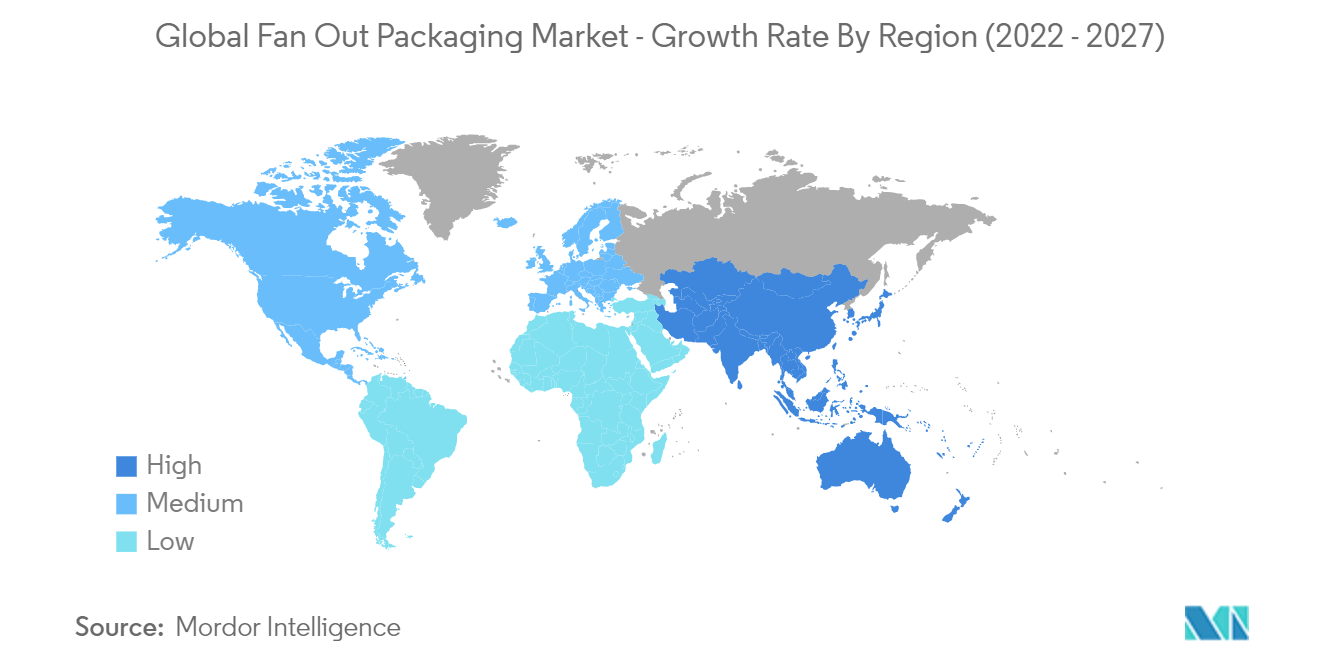

Taiwan wird einen bedeutenden Marktanteil halten

- Taiwan beherbergt einige der größten Halbleiterhersteller, die die Nachfrage nach fortschrittlichen Halbleiterverpackungen, insbesondere in PLPs, ankurbeln. Laut einer staatlichen Denkfabrik, dem Science and Technology International Strategy Center, soll Taiwans Produktion im Jahr 2021 um 25,9 % auf 147 Milliarden US-Dollar wachsen.

- Nach Angaben der Semiconductor Industry Association (SIA) erwirtschaftet der asiatisch-pazifische Raum mehr als 50 % des weltweiten Umsatzes mit Halbleitern; Dies wiederum bietet taiwanesischen Anbietern die Möglichkeit, FOWLP für zunehmende Halbleiteranwendungen zu liefern.

- Die meisten Unternehmen im Land erweitern ihre Produktionskapazität für Fan-out-Verpackungen, was voraussichtlich die Exporte weiter steigern und zur Entwicklung des lokalen Marktes beitragen wird. Beispielsweise wird Intel, das kürzlich seine Rückkehr in die Gießereiindustrie angekündigt hat, gleichzeitig 3,5 Milliarden US-Dollar in New Mexico investieren, um eine Halbleiterverpackungsfabrik zu errichten, die in der zweiten Hälfte des Jahres 2022 ihren Betrieb aufnehmen wird.

- Darüber hinaus begann ASE, ein reines Halbleiter-Post-Processing-Unternehmen (OAST), im Juni 2021 mit der Investition in fortschrittliche Verpackungsanlagen als Reaktion auf die Angebots- und Nachfrageknappheit bei Halbleitern. Das Unternehmen beschleunigt die Expansion durch den Kauf einer großen Menge an Halbleiterfertigungsanlagen für WLP- und PLP-Prozesse von HANMI Semiconductor.

- Darüber hinaus hat der wachsende Markt für drahtlose Kommunikation und Hochleistungsrechnen der fünften Generation (5G) den Herstellern die Entwicklung neuer Technologien ermöglicht. Als alleiniger Marktführer im High-Density-Fanout-Segment plant TSMC beispielsweise, sein FO-WLP-Segment auf Technologien wie inFO-Antenna-in-Package (AiP) und inFO-on-Substrate (oS) auszudehnen.