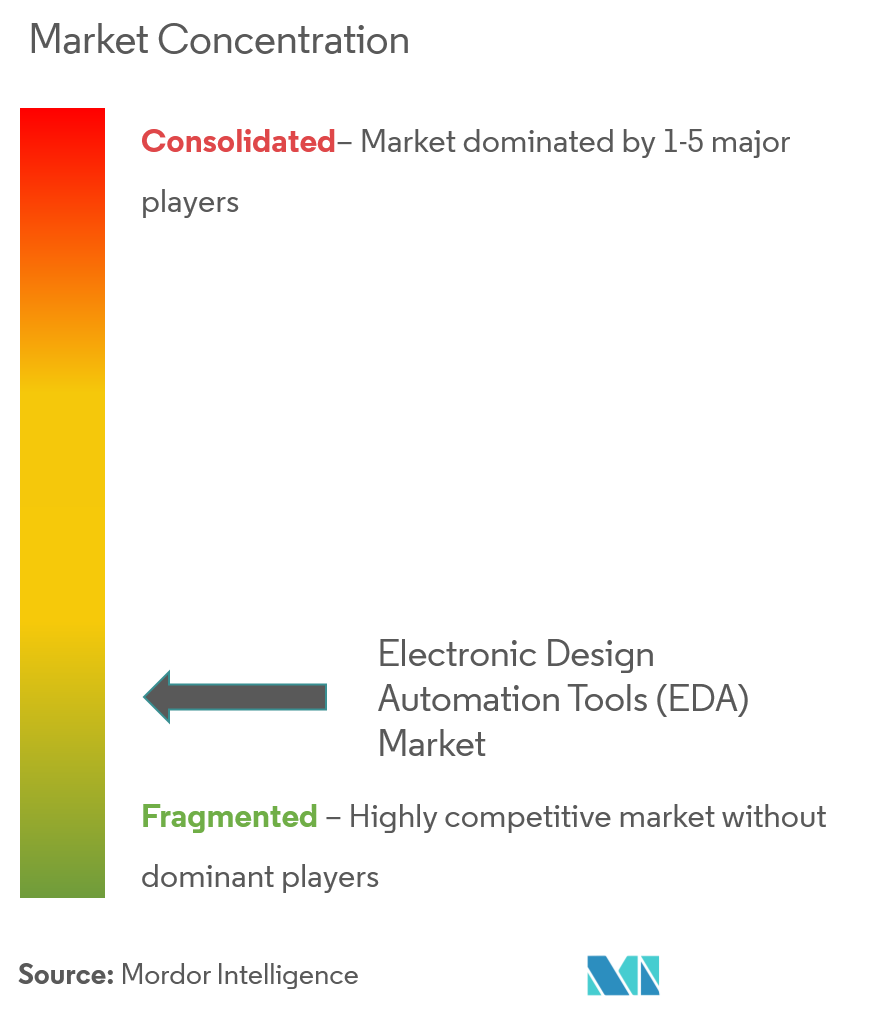

Marktanteil von Globale Electronic Design Automation Tools (EDA) Industrie

Der EDA-Markt ist stark fragmentiert. Neue Möglichkeiten in den Bereichen Automobil, IoT, künstliche Intelligenz und virtuelle/erweiterte Realität haben es Halbleiterunternehmen in allen Phasen des IC-Produktionszyklus ermöglicht, zu florieren und beträchtliche Umsatzsteigerungen zu erzielen. Dies geschah trotz erheblicher Steigerungen der Chipleistung, jedoch bei relativ unveränderten Stückverkaufspreisen. Zu den wichtigsten Akteuren der Branche gehören ANSYS, Cadence Design Systems, Synopsis, Keysight Technologies usw. Einige der wichtigsten Entwicklungen auf dem EDA-Markt sind wie folgt:

- März 2022 – Synopsys hat die Einführung eines neuen EDA-Bereitstellungsmodells (Electronic Design Automation) angekündigt, das für die Cloud konzipiert ist und ein beispielloses Maß an Chip- und Systemdesign-Flexibilität durch ein Pay-as-you-go-System aus einer Hand bietet Ansatz. Mit einer voroptimierten Infrastruktur auf Microsoft Azure bietet Synopsys Cloud Zugriff auf die Cloud-optimierten Design- und Verifizierungstechnologien des Unternehmens, die das zunehmende Maß an gegenseitigen Abhängigkeiten bei der Chipentwicklung berücksichtigen.

- Juni 2021 – Xilinx, Inc. stellt Vivado ML Editions vor, ein FPGA-EDA-Toolpaket, das auf Optimierungstechniken des maschinellen Lernens (ML) und fortschrittlichen teambasierten Designverfahren für erhebliche Designzeit- und Kosteneinsparungen basiert. Wenn man die neuen Vivado ML Editions mit den bestehenden Vivado HLx Editions vergleicht, bietet erstere eine fünfmal schnellere Kompilierungszeit und revolutionäre Verbesserungen der Ergebnisqualität (QoR), die bei schwierigen Designs durchschnittlich 10 % betragen.

- Juni 2021 – Aldec Inc. hat die HES-DVM Proto Cloud Edition (CE) auf den Markt gebracht. Es ist über Amazon Web Service (AWS) verfügbar. HES-DVM Proto CE kann für das FPGA-basierte Prototyping von SoC-/ASIC-Designs verwendet werden und konzentriert sich auf die automatisierte Designpartitionierung, um die Bereitstellungszeit erheblich zu verkürzen, wenn bis zu vier FPGAs für die Unterbringung eines Designs erforderlich sind.

- Mai 2021 – Cadence Design Systems kündigte Low-Power-IP für die PCI Express 5.0-Spezifikation an, die auf Hyperscale-Computing-, Netzwerk- und Speicheranwendungen abzielt, die auf der TSMC N5-Prozesstechnologie erstellt werden. Darüber hinaus besteht die PCIe 5.0-Technologie aus einem PHY, einem Companion-Controller und Verification IP (VIP), die auf SoC-Designs für eine sehr hohe Bandbreite zur Anpassung an die Anwendungen ausgerichtet sind.

Marktführer für EDA-Tools

-

ANSYS Inc.

-

Cadence Design Systems Inc.

-

Keysight Technologies Inc

-

Synopsys Inc.

-

Xilinx Inc.

*Haftungsausschluss: Hauptakteure in keiner bestimmten Reihenfolge sortiert